Page 117 - 《应用声学》2022年第3期

P. 117

第 41 卷 第 3 期 陈谋等: 面向电容式微机械超声换能器器件的 32 通道收发电路设计与测试 439

OUT1

CMUT1 CMUT2 CMUT32

LTC6269-10(1)

C 1

V DC

. . . OUT2

HVOUT1 HVOUT2 HVOUT32 OUT3

LTC6269-10(2)

LVOUT1

T/R1

OUT4

MAX14808 MAX14808 LVOUT2

T/R2

FPGA . . . . . .

MAX14808 MAX14808

LVOUT32

T/R32 OUT31

LTC6269-10(16)

㜹ߢ⭥䐟

OUT32

ᡵஊܸႃ

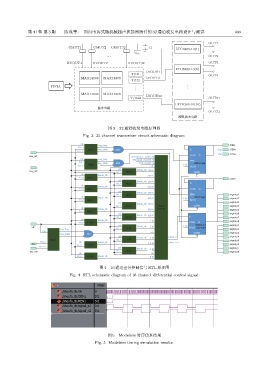

图 3 32 通道收发电路原理图

Fig. 3 32 channel transceiver circuit schematic diagram

Clk key_flag REN

Rst_n

filter1 key_state EN1 D 1’h0 OEN1

key_in

1’h0 REN1

key_in1 32’h1f4 time_cnt[31..0] >CLK Q

Clk key_flag 6’hfsignal_mode[5..0]

Rst_n key_state EN2 6’h5 count[5..0] ENA

REN~reg0

filter2 1’h0

key_in clk SCLR

clk divide_clk

key_in2 100 K 100 K

rst_n CLRN

clk divide_clk 200 K

rst_n 200 K OEN

clk divide_clk 300 K

rst_n 300 K D

clk divide_clk 400 K

rst_n 400 K >CLK Q

clk divide_clk 500 K

rst_n 500 K ENA signal p1

clk divide_clk 600 K OEN~reg0 signal p2

rst_n 600 K 1’h0 SCLR

clk signal p3

divide_clk 700 K

rst_n 700 K Signal CLRN signal p4

clk divide_clk 800 K choose

rst_n 800 K signal p5

clk divide_clk signal p6

rst_n 900 K 900 K D signal p7

clk divide_clk 1 M

rst_n 1.0 M >CLK Q signal p8

clk Signal_p1 signal p1

clk rst_n divide_clk 2 M 1’h0 SCLR_reg~reg0

key_flag 2 M signal p2

Clk EN

key_state EN CLRN signal p3

clk divide_clk 3 M pluse_o signal p4

filter0 rst_n 3 M signal p5

Rst_n clk divide_clk pluse_o_n

rst 3.5 M signal p6

rst_n 3.5 M

key_in

clk signal p7

divide_clk 4 M

key_in0 rst_n 4 M signal p8

clk rst

rst_n 5.0 M divide_clk 5 M

图 4 16 通道差分控制信号 RTL 原理图

Fig. 4 RTL schematic diagram of 16 channel differential control signal

图 5 Modelsim 时序仿真结果

Fig. 5 Modelsim timing simulation results