Page 93 - 《应用声学》2024年第6期

P. 93

第 43 卷 第 6 期 孟新宝等: 小型化相控参量阵声呐发射系统设计与实现 1269

公式 (9),点划线对应可选择的最大半径,虚线与

2 发射系统整体装配

实线交点处即为当前 N c 值对应的最佳电容半径及

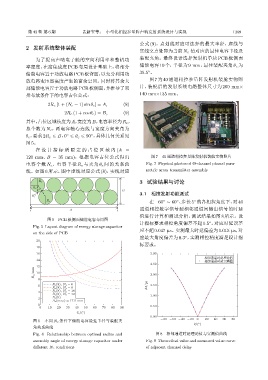

为了提高声呐电子舱的空间利用率和整机功 装配夹角。最终设计选择发射机单块 PCB 板侧面

率密度,在高集成度 PCB 布局设计基础上,将部分 储能电容 10 个,半径为 9 mm,最佳装配夹角 θ c 为

◦

储能电容置于功放电路PCB板背面,以充分利用功 35.5 。

放电路变压器高度产生的富余空间。同时将其余大 图 7 为 40 通道相控参量阵发射机装舱实物照

部储能电容置于功放电路PCB板侧面,并推导了双 片,装配后的发射系统电路整体尺寸为 200 mm×

排布放条件下的电容占位公式: 140 mm×135 mm。

2R c [1 + (N c − 1) sin θ c ] = A, (8)

2R c (1 + cos θ c ) = B, (9)

其中,占位区域长度为A,宽度为B,电容半径为R c ,

总个数为 N c ,两电容轴心连线与宽度方向夹角为

θ c ,要求 2R c 6 B,0 6 θ c 6 90 ,具体几何关系见

◦

◦

图5。

在 设 计 指 标 所 限 定 的 占 位 区 域 内 (A =

120 mm、B = 35 mm),根据电容占位公式得出 图 7 40 通道相控参量阵发射机装舱实物照片

电容个数 N c 、电容半径 R c 与夹角 θ c 间的关系曲 Fig. 7 Physical photos of 40-channel phased para-

线。如图 6 所示,图中虚线对应公式 (8),实线对应 metric array transmitter assembly

R c 3 试验结果与讨论

R c

B

3.1 相控发射功能测试

θ c

在 −60 ∼ 60 、步长 5 的各相控角度下,对 40

◦

R c

◦

◦

通道相控数字信号源相邻通道间输出信号的时延

A

值进行计算和测试分析,测试结果如图 8 所示。设

图 5 PCB 板侧面储能电容布局图

计指标要求相控角度偏差不超 0.5 ,对应时延误差

◦

Fig. 5 Layout diagram of energy storage capacitor

应不超 0.047 µs。实测最大时延偏差为0.015 µs,对

on the side of PCB

应最大角度偏差为 0.3 ,实测相控精度满足设计指

◦

20

标要求。

18

16 3.00

ᄱᤰ᥋णေϙ

14 ᄱᤰ᥋णࠄϙ

2.50

12

R c /mm 10 2.00

8

R c (8), N c =6 1.50

6 Dt/ms

R c (8), N c =8

R c (8), N c =10

4

R c (8), N c =12 1.00

2 R c(9)

R c (max)=17.5 mm

0 0.50

0 10 20 30 40 50 60 70 80 90

θ c /(O)

0.00

图 6 不同 N c 条件下储能电容最佳半径与装配夹 -80 -60 -40 -20 0 20 40 60 80

θ/(O)

角关系曲线

Fig. 6 Relationship between optimal radius and 图 8 相邻通道时延理论值与实测值曲线

assembly angle of energy storage capacitor under Fig. 8 Theoretical value and measured value curve

different N c conditions of adjacent channel delay