Page 174 - 《应用声学》2022年第1期

P. 174

170 2022 年 1 月

VPPA 因源端电流流向与反射回源端的电流流向相

MAX14808

cc0 lvout1 反,由欧姆定律与串联电流特性可得

cc1 Ā

T/RनТ

FPGA ldo_en lvout8

(XC6SLX9̶ sync Ā V 1 /Z 1 − V 3 /Z 1 = (V 1 + V 3 )/Z 2 . (2)

clk

mode0 out1 通过式(1) ∼ (2)可得反射系数r 与传输系数t:

mode1 Ā

V 3 Z 2 − Z 1 V 2 2Z 2

IO_DINNn out8 r = = , t = = . (3)

DINNn

IO_DINPn V 1 Z 2 + Z 1 V 1 Z 2 + Z 1

DINPn

VNNA 由公式 (3) 可知,当 Z 1 大于 Z 2 时,末端的电压

图 3 MAX14808 的简化逻辑控制图 V 2 小于源端电压 V 1 ;反之,V 2 大于 V 1 。因源端阻

Fig. 3 Simplified schematic for MAX14808 logical 值不为零,所以电压信号在源端与末端之间存在

control 多次反射,导致过冲现象的出现。过冲现象会造成

CMUT的损坏,需要针对此现象提出解决方法。

2.2 电源模块的优化设计

本文采用源端串联匹配电阻的方法,消除信号

驱动电路需要多个供电电压。结合 CMUT 的

的过冲现象。通过不同阻值的电阻进行匹配。由

驱动需求,优化设计了电源模块。使用一个直流电

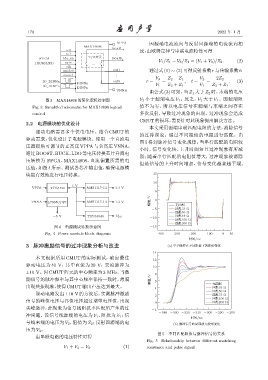

图 5 得到脉冲信号变化规律,当串行匹配的电阻较

压源提供可调节的正高压 VPPA 与负高压 VNNA,

小时,信号变化快、上升时间短且过冲现象有所减

通过BOOST、BUCK、LDO等电压转换芯片升降电

弱;随着串行匹配的电阻值增大,过冲现象被消除

压转换为 FPGA、MAX14808、直流偏置所需的电

但是信号的上升时间增加、信号变化越来越平缓。

压值,如图 4 所示。测试各芯片输出值,确保电源模

块能有效地进行电压转换。 15

10

5 V

VPPA TPS5430 AMS1117-3.3 3.3 V

5

ࣨϙ/V 0

VNNA L7905CD2T AMS1117-1.2 1.2 V Ӝᦡ

-5 Ӝᦡ33 W

Ӝᦡ50 W

-5 V TPS55340 V DC Ӝᦡ75 W

-10

Ӝᦡ100 W

Ӝᦡ200 W

图 4 电源模块转换示意图 -15

Fig. 4 Power module block diagram -400 -300 -200 -100 0 50

ᫎ/ns

3 脉冲激励信号的过冲现象分析与改进 (a) ӭ˔ᑢфښˀՏϙʾᄊฉॎԫӑ

14

本文根据所用 CMUT 的实际测试,确定最佳 12

驱动电压为 40 V,其中直流为 20 V,交流脉冲为

10

±10 V。因 CMUT 阵元的中心频率为 3 MHz,当激 8

励信号的脉冲频率与其中心频率保持一致时,薄膜 ࣨϙ/V 6

出现共振现象,使得CMUT输出声压达到最大。 4 Ӝᦡ

Ӝᦡ33 W

Ӝᦡ50 W

驱动电路发出 ±10 V 的方波后,实测脉冲激励 2 Ӝᦡ75 W

Ӝᦡ100 W

信号的峰值电压与谷值电压超过期望电压值,出现 0 Ӝᦡ200 W

尖峰脉冲,此现象为信号线阻抗不匹配所产生的过 -2

-340 -330 -320 -310 -300 -290 -280

冲问题。设信号线源端的电压为 V 1 ,阻抗为 Z 1 ;信

ᫎ/ns

号线末端的电压为 V 2 ,阻值为 Z 2 ;反射回源端的电 (b) ᑢфηՂᄊࡍᦊஊܸฉॎԫӑ

压为V 3 。

图 5 不同匹配阻值与脉冲信号的关系

由串联电路的电压特性可得

Fig. 5 Relationship between different matching

V 1 + V 3 = V 2 . (1) resistance and pulse signal