Page 72 - 《应用声学》2023年第3期

P. 72

510 2023 年 5 月

FPGAܱᦊவՔ FPGAᔇྟЯᦊ

PLL᧿

FPGAЯᦊவՔ

SCCBү

NCOߚ FIRߚ ฉ֗

ᕥ٨ OOKូ҄ ࣜᤰฉ D/Aᣁ૱ ஊܸႃ ԧηՂ

SCCB OV7725

឴

SCCBᦡᎶ

ϸ݀ SDRAM

ڏϸ᧔ᬷ и ҄٨

ϸ݀

图 2 系统发送端结构

Fig. 2 Structure of the system sender

ϸጉག ϸጉག ϸጉག ϸጉག

ϸጉག1 ĀĀ ĀĀ

n-1 n n⇁ N

ᡑݽͯ Տ൦ͯ ͯ ಣᰎͯ ϣൣͯ δઐ

ᫎᬦͯ

2 bit 8 bit 16 bit 2 bit 2 bit 2 bit

图 3 像素点的数据结构

Fig. 3 Data structure of pixels

FPGAܱᦊவՔ FPGAᔇྟЯᦊ

PLL᧿

FPGAЯᦊவՔ

FIRߚ

ͯՏ൦ OOKᝍូ Ͱᤰฉ

VGAү

и ᒭᤠऄ۫ ஊܸ֗

௭ᇨ٨ VGA҄ ឴ SDRAM کᛦ٨ A/Dᣁ૱ ฉႃ ଌஆηՂ

҄٨

图 4 系统接收端结构

Fig. 4 Structure of system receiver

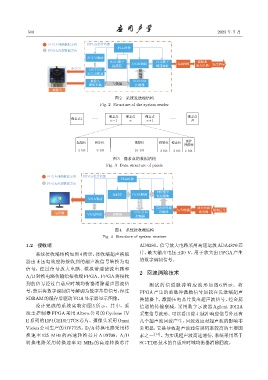

1.2 接收端 AD9280。信号放大电路采用高速运放 ADA4870芯

系统接收端结构如图 4 所示,接收端超声换能 片,最大输出电压 ±20 V,用于放大由 FPGA 产生

器由正压电效应将接收到的超声波信号转换为电 的数字调制信号。

信号,经过信号放大电路、模拟带通滤波电路和

2 回波消除技术

A/D转换电路传输给接收端FPGA。FPGA将接收

到的信号经过自适应时域均衡器消除超声回波信 测试的信道脉冲响应波形如图 6 所示。 将

号,然后将数字调制信号解调为数字基带信号,经过 FPGA 产生的单脉冲激励信号加载在发送端超声

SDRAM的缓存后驱动VGA显示器显示图像。 换能器上,激励压电晶片发出超声波信号,经金属

设计完成的系统实物如图 5 所示,其中,系 信道的传输衰减,采用数字示波器 Agilent 2012A

统主控制器 FPGA 采用 Altera 公司的 Cyclone IV 采集信号波形。可以看出除主脉冲响应信号外还有

E 系列的 EP4CE16F17C8 芯片。摄像头采用 Omni 几个超声波回波产生,回波效应对超声波的影响非

Vision 公司生产的 OV7725。D/A 转换电路采用转 常明显,它是导致超声波通信误码率较高的主要因

换速率 125 MHz 的高速转换芯片 AD9708,A/D 素之一 [14] 。为实现超声波高速通信,系统采用基于

转换电路采用转换速率 32 MHz 的高速转换芯片 SC-TDE技术的自适应时域均衡器消除回波。