Page 27 - 201806

P. 27

第 37 卷 第 6 期 张浩等: 基于 FPGA 的高强度聚焦超声相位控制系统设计 857

图 4 FPGA 开发板

Fig. 4 FPGA development board

2.3.1 粗相控延时

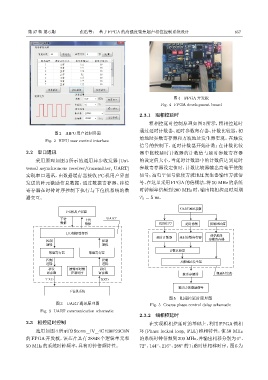

粗相控延时控制原理如图 5 所示,粗相控延时

通过延时计数器、延时参数寄存器、计数比较器、初

图 2 HIFU 用户控制界面

始地址参数寄存器和方波地址发生器实现。在触发

Fig. 2 HIFU user control interface

信号的控制下,延时计数器开始计数;在计数比较

2.2 串口通讯 器中比较延时计数器的计数值与延时参数寄存器

采用原理如图 3 所示的通用异步收发器 (Uni- 的设定值大小,当延时计数器中的计数值达到延时

versal asynchronous receiver/transmitter, UART) 参数寄存器设定值时,计数比较器输出高电平使能

实现串口通讯,由数据缓存器接收 PC 机用户界面 信号;高电平信号能使方波地址发生器输出方波信

发送的阵元激励信息数据,通过数据寄存器、移位 号,在这里采用FPGA的倍频法,将50 MHz的系统

寄存器在时钟时序控制下执行与下位机系统的数 时钟频率倍频到 200 MHz 时,输出粗相控延时周期

据交互。 T 5 = 5 ns。

6"35ᤰԠ

PCၹਗ਼ႍ᭧

ʾ͜ ʽ͜ UART

҄ηՂ णԠ Ѻݽڡڧϙ

I/Oᎁߛ٨

णᝠ٨ णԠ࠙ߛ٨ Ѻݽڡڧ

҄ ҄ Ԡ࠙ߛ٨

ᣤ ᣤ

ᝠඋᣗ٨

࠙ߛ٨ ࠙ߛ٨

҄ ҄ வฉڡڧԧၷ٨

ᣤ ᣤ

ረͯ ฉྲဋ᧿ ረͯ

࠙ߛ٨ ҄ऀ ࠙ߛ٨ ฉॎߛϲ٨ ዤणࠄဘ

TXD RXD

ᣥѣவฉ༏ҵηՂ

ʾͯጇፒ

图 5 粗相控延时原理图

图 3 UART 通讯原理图 Fig. 5 Coarse phase control delay schematic

Fig. 3 UART communication schematic

2.3.2 细相控延时

2.3 相控延时控制 在实现粗相控延时的基础上,利用 FPGA 锁相

选用如图 4 所示的 Storm_IV_4CE30F23C8N 环 (Phase locked loop, PLL) 移相特性,使 50 MHz

的 FPGA 开发板,该芯片具有 28848 个逻辑单元和 的系统时钟倍频到200 MHz,并输出相移分别为0 、

◦

50 MHz的系统时钟频率,具有时钟倍频特性。 72 、144 、216 、288 的五路时钟相移时序。图6为

◦

◦

◦

◦