Page 28 - 201806

P. 28

858 2018 年 11 月

5 ns 1ns 1ns 1ns 1ns 1ns

C 0

C 1

C 2

C 3

C 4

图 6 细相控延时锁相环输出时序图

Fig. 6 Meticulous phase-locked delay PLL output timing diagram

输出周期均为5 ns的C 0 ∼C 4 五路时钟,每一路相对 ilent 示波器 (DSOX4052A/500M/5GSa/s) 进行显

上一路相移均为72 ,实现1 ns的细相控延时。 示检测。

◦

通过粗相控延时 T 5 = 5 ns 和细相控延时 当两通道输出相位信号频率均为 0.8 MHz、

T 1 = 1 ns实现相控阵元延时为 占空比分别为 49.60% 和 49.57% 时,检测结果如

图 7(a)所示。由图7(a)可知,与设定的频率、占空比

T delay = m × T 5 + n × T 1 , (1)

相比,误差均小于 0.5%。通道 1 和通道 2 设置延时

式 (1) 中,m、n 分别为所需粗相控延时 T 5 个数和细

分别为100 ns和101 ns,两通道实测相移为0.3 ,延

◦

相控延时T 1 个数。

时时间为 1.2 ns。由图 7(a) 的局部放大图图 7(b) 可

3 结果 知延时分辨率为1 ns。

当工作频率为1 MHz、占空比分别为49.92%和

3.1 检测结果 49.88%时,检测结果如图7(c)所示。由图7(c)可知,

3.1.1 不同频率 与设计设定的频率、占空比相比,误差均小于 0.5%。

基于 FPGA 设计制作的 HIFU 相位控制系统 通道1和通道2设置延时分别为102 ns和103 ns,两

通过 PC 机用户界面经串口将延时数据发送到 通道实测相移为0.4 ,延时时间为 1.2 ns。由图 7(c)

◦

FPGA 并产生方波激励信号。该方波信号经 Ag- 的局部放大图图7(d)可知延时分辨率为1 ns。

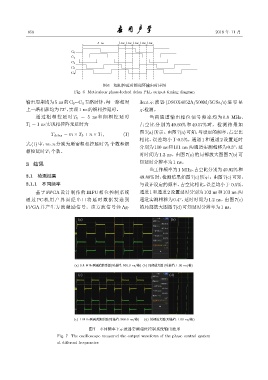

(a) (b)

(a) 0.8 MHzːᤰ᥋ฉॎڏ(۳ೂ 500.0 ns/ಫ) (b) ࡍᦊஊܸڏ (۳ೂ 1.00 ns/ಫ)

(c) (d)

(c) 1 MHzːᤰ᥋ฉॎڏ(۳ೂ 500.0 ns/ಫ) (d) ࡍᦊஊܸڏ(۳ೂ 1.00 ns/ಫ)

图 7 不同频率下示波器实测相位控制系统输出波形

Fig. 7 The oscilloscope measured the output waveform of the phase control system

at different frequencies