Page 72 - 《应用声学》2023年第4期

P. 72

734 2023 年 7 月

限转换和正余弦转换模块,坐标转换和相位转换模

4 FPGA实现与实验验证

块将迭代角度范围扩展至 0 ∼ 360 。两路信号处

◦

◦

4.1 FPGA实现方案 理电路,均采用同一个 CORDIC 模块产生的正交

本振信号来实现同频同相。使用 IIR 滤波给两路信

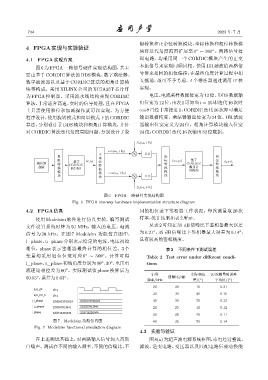

图 6 为 FPGA 一路信号硬件实现结构图,其主

要由基于 CORDIC 算法的 DDS 模块、数字乘法器、 号带来相同的相位偏移,在最终角度计算过程中相

数字滤波器以及基于 CORDIC 算法的相角计算模 互抵消,故可不予考虑。4 个乘法器通过调用 IP 核

块等构成。采用 XILINX 公司的 XC7A35T 芯片作 实现。

为 FPGA 控制器。采用流水线结构实现 CORDIC 电压、电流采样数据位宽为12位。DDS数据输

算法,非常适合高速、实时的信号处理,且在 FPGA 出位宽为12位,由表1 可知当 i = 15 即迭代 16次时

上只需使用移位和加减操作就可以实现。为方便 cos θ 已经非常接近 1,CORDIC迭代 16次即可满足

程序设计,使用旋转模式和向量模式下的 CORDIC 输出数据精度。乘法器输出位宽为 24 位。IIR 滤波

算法,分别设计了 DDS 模块和相角计算模块,并针 器输出位宽定义为 24 位。相角计算模块输入位宽

对CORDIC算法迭代角度局限问题,分别设计了象 24位,CORDIC迭代16次输出32位数据。

S a (ω n +θ )

sin(ω n+θ )

IIR

៶ گ ᄱ

ᬍ ۳̆ ↼x֒y↽ ಖ ↼x ֒y ↽ ۳̆ ͯ

ᄱͯግ ᣁ CORDIC ऺ ᣁ CORDIC ᣁ θ +θ

ҫ٨ ૱ ᄊDDS ᣁ ૱ ᄱᝈᝠ ૱

૱

വ വ cos(ω n+θ ) വ ካവڱ വ

ڱ ڱ IIR ڱ ڱ

S a (ω n +θ )

图 6 FPGA 一路硬件实现结构图

Fig. 6 FPGA one-way hardware implementation structure diagram

4.2 FPGA仿真 同的相位差下鉴相器工作状况。每次测量取 20 次

使用 Modelsim 软件进行仿真实验,编写测试 样本,统计结果如表2所示。

文件设置系统时钟为 50 MHz,输入的电压、电流 从表 2 可知在 30 dB 信噪比下鉴相器最大误差

◦

◦

信号为 20 kHz。在图 7 Modelsim 功能仿真图中, 为 0.21 ,35 dB 信噪比下鉴相器最大误差为 0.14 ,

i_phase、u_phase 分别表示给定的电流、电压初始 具有较高的鉴相精度。

相位,phase 表示鉴相器最终计算的相位差。3 个 表 2 不同条件下测试误差

变量均采用 32 位位宽对应 0 ∼ 360 。计算可得 Table 2 Test error under different condi-

◦

◦

i_phase、u_phase初始角度分别为90 、30 ,电压电 tions

◦

◦

流理论相位差为 60 。实际测试值 phase 换算后为

◦

信号 实际相位 20 次测量的误差

60.03 ,误差为0.03 。 信噪比/dB

◦

◦

频率/kHz 差/( ) 平均值/( )

◦

◦

20 30 10 0.21

30 30 40 0.15

40 30 70 0.17

20 35 10 0.12

30 35 40 0.11

图 7 Modelsim 功能仿真图 40 35 70 0.14

Fig. 7 Modelsim functional simulation diagram

4.3 实验与验证

在上述测试基础上,对两路输入信号加入高斯 图8(a)为超声波电源系统框图,市电经过整流、

白噪声。测试在不同的输入频率、不同的信噪比、不 滤波、逆变电路、变压器以及匹配电路后驱动换能