Page 212 - 《应用声学》2025年第1期

P. 212

208 2025 年 1 月

1464 235

488 488

200~400 Hzѵ

φ118 φ145

200

488

1200 215

300 300 300 400~800 Hzѵ

φ115 φ98

150

300

1050 118

150 150 150 150 150 150

φ70

100

800~1600 Hzѵ

525

15

75 75 75 75 75 75

75 800~1600 Hzѵ

75 φ48

262.5

37.5

23

55 3200~6400 Hzѵ

R14.5

37.5

173

23

55 6400~12800 Hzѵ

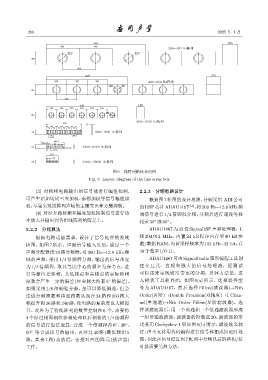

图 6 线阵列箱体布局图

Fig. 6 Layout diagram of the line array box

(3) 对移相电路输出的信号能进行幅值控制, 2.2.3 分频电路设计

可产生诸如切比雪夫加权、泰勒加权等信号幅值加 根据图 7 框图的设计思路,分频采用 ADI 公司

权,尽量实现线阵列声场的主瓣突出和旁瓣抑制。 的DSP芯片ADAU1467 [23] ,将200 Hz∼12.8 kHz频

(4) 对经多路移相和幅度加权控制信号进行功 域信号进行 1/4 倍频程分频,分频后进行逐段等移

率放大并输出到各组线阵列的阵元上。 相差30 或60 。

◦

◦

2.2.2 分频算法 ADAU1467为32位SigmaDSP声频处理器,主

根据电路功能需求,设计了信号处理的系统 频 294.912 MHz,内置 24 kB 程序内存和 80 kB 参

框图,如图 7 所示。声频信号输入以后,通过一个 数/数据 RAM,内置采样频率为 192 kHz、32 bit,有

声频分配器接 24路分频器,对200 Hz∼12.8 kHz 频 48个数字I/O口。

域的声频,采用 1/4 倍频程分频,输出的信号带宽 ADAU1467可由SigmaStudio图形编程工具创

为 1/4 倍频程,取其等比中心的频率为参考点,进 建交互式、直观和强大的信号处理流。经测试

行等相位差移相,其低频点和高频点的实际移相 可以用来实现较窄带宽的分频,具体方法是:进

度数会产生一定的偏差 (经实测大约有 5 的偏差)。 入树状工具箱界面,如图 8(a) 所示,选择器件型

◦

如果采用 1/6 倍频程分频,虽可以降低偏差,但会 号为 ADAU1467,然后选择 Fillers(滤波器)→Nth

造成分频路数和移相路数从现在 24 路和 160 路大 Order(N 阶)→Double Precision(双精度)→1 Chan-

幅提升到 36 路和 240 路,使电路的复杂度也大幅提 nel(单通道)→Nth Order Fillers(N 阶滤波器)。选

升。此外为了将线阵列的数量控制在 6 个,需要将 择该滤波器后,用一个高通和一个低通滤波器形成

4 个经过相同相位移相处理以后相邻的 1/4 倍频程 一组带通滤波器,滤波器的阶数选 20,滤波器的形

的信号进行加法运算,合成一个倍频程内 0 、30 、 式采用 Chebyshev 1 型如图 8(b) 所示,滤波效果较

◦

◦

60 等合成信号的输出,再经过 40 路 (最低频组 5 好,但不支持用代码编程进行信号移相或短延时处

◦

路,其余 7 路) 功放后,去推对应的阵元 (扬声器) 理。因此在信号经过图7框图中分频以后的移相/延

工作。 时就需要另想方法。