Page 80 - 《应用声学》2025年第1期

P. 80

76 2025 年 1 月

占印制板面积等于管芯面积,封装比例等于或接近

0 引言

于 1,WLP 封装厚度薄 (只有芯片厚度加上衬底层

的厚度,通常高度为 0.4 ∼ 1.2 mm),质量小,体积

为了增加探测精度、减小发射费效比,卫星

小,引出端引线短,可以提高整机的封装密度。

通信、雷达探测、电子对抗、移动通信等射频电子

(3) 因 WLP 从芯片上的焊盘到封装引出端的

设备中的装备系统正在向小型化、集成化方向发

展 [1] 。声表面波 (Surface acoustic wave, SAW) 滤 距离短,所以其引线电感、引线电阻等寄生参数小,

波器由于具有体积小、一致性好的巨大优势被广 而引出端焊盘又都在芯片下方,因此 WLP 的电热

泛应用 [2] 。在雷达 T/R 组件上,滤波器用来抑制杂 性能较好。

波和干扰,通常一个阵列上需要几千甚至上万只滤 (4) 制作 WLP 可采用大量现有成熟的半导体

工艺技术,如溅射、光刻、芯片上多层布线、电镀、分

波器;同时为保证天线辐射波束的高指向性、满足

割等。

小旁瓣的要求,每个 T/R 组件中心的距离小于半

(5) WLP具备可靠性高、电磁兼容性好等优点。

个波长,因而留给滤波器的尺寸越来越小 (通常在

3 mm × 3 mm 以下),即要求滤波器向小型化和集 因此,本文对 SAW 滤波器的 WLP 技术进行

成化方向发展 [3] 。 研究。

然而,传统的金属封装和陶瓷表面贴装的SAW

1 方案设计

滤波器已经无法满足装备进一步小型化的要求,且

SAW裸芯片表面易损伤,铝电极和压电材料无法实 SAW 芯片 WLP 三维封装结构设计是 SAW 滤

现混合集成,难以实现系统级封装和高密度集成 [4] 。 波器 WLP 首要课题,决定了 WLP 的工艺路线、电

为了满足多功能SAW芯片集成技术的发展要求,亟 气互联、封装尺寸和可靠性,并最终决定 WLP 的

需进行下一代超小型SAW器件及其封装技术研究。 SAW芯片的性能指标。

目前,最新的芯片级封装技术为晶圆级芯片封 衬底设计:芯片衬底考虑 L 波段和降低键合时

装 (Wafer level chip size packing,简称 WLCSP 或 压电和热电效应影响,采用高声速、损耗小、大机电

WLP),封装面积与芯片面积大小相当,器件尺寸可 耦合的还原处理的 LT 基片,对于带宽的指标采用

达0.8 mm × 0.6 mm × 0.3 mm,达到了目前可能的 还原处理 LN 基片。封装衬底均采用与芯片衬底一

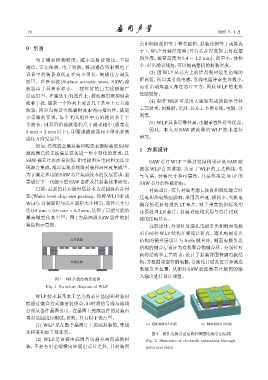

最高微型化水平 [5] 。图 1 为晶圆级 SAW 器件的封 致的压电基片。

装结构示意图。 互联设计:分别针对通孔电极引出和侧面电极

引出两种 WLP 结构开展设计研究。通孔电极引出

ᔇྟఃړ 结构的键合层设计为 AuSn 键合环,侧面电极引出

结构的键合层设计为有机聚合物键合环。分别针对

两种结构和工艺特点,设计了封装背面管脚电极结

࠰ᜉఃړ 构,并根据背面管脚电极,分别设计通孔位置和侧边

电极引出位置,从而对 SAW 滤波器芯片版图的输

入输出进行设计调整。

图 1 WLP 的结构示意图

Fig. 1 Structure diagram of WLP

WLP 技术其基本工艺为将芯片晶圆和封装衬

底通过键合方式做密封结合,同时将信号线与地线

分别从器件晶圆引出。在晶圆上完成器件的封装后

再对晶圆进行测试、切割。具有以下优点 [6] :

(1) WLP 是在整个晶圆片上完成封装的,集成 (a) ᤰߘႃౝळѣፇ (b) Ο᭧ႃౝळѣፇ

化程度和加工效率高。 图 2 通孔电极引出结构和侧面电极引出结构

(2) WLP 是直接由晶圆片切割分离而成的封 Fig. 2 Structure of electrode extraction through

装,不会有引出端横向伸展出芯片之外,其封装所 holes and sides