Page 194 - 《应用声学》2025年第3期

P. 194

728 2025 年 5 月

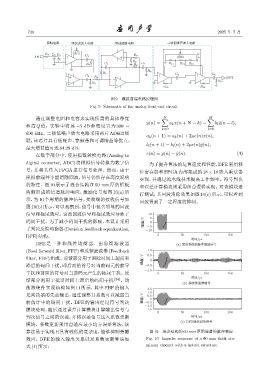

ᬍࣨႃ ʷጟ́᛫ஊܸႃ ࣜᤰฉႃ ̄ጟͰ٪ܦஊܸႃ

-

SR1

R 1 D D

IN + C + R 7 SR2 5 V

- R 6

R 2 C R 8 C R 11 R 12 R 13

R 9

R 5

+ C + C

+ C R 4 OUT

+ - -

- R 3 R 15

-

R 10 R 14

图 9 模拟前端电路原理图

Fig. 9 Schematic of the analog front-end circuit

通过调整电阻和电容来实现所需的具体带宽 ∑ ∑

N

M

y(n) = a k x(n + N − k) − b l ˆy(n − l),

和高 Q 值,实验中将其 −3 dB 带宽设置为 300 ∼

k=0 l=0

600 kHz。二级低噪声放大电路采用两片 AD603 级

a k (n + 1) = a k (n) + 2µe(n)x(n),

联,该芯片具有低噪声、宽频带和可调增益等优点,

b l (n + 1) = b l (n) + 2µe(n)ˆy(n),

最大增益值可达84.28 dB。

在数字部分中,使用模数转换电路 (Analog to e(n) = y(n) − ˆy(n). (4)

digital converter, ADC) 将模拟信号转换为数字信 为了提升算法的运算速度和性能,DFE采用移

号,并将其传入 FPGA 进行信号处理。然而,由于 位寄存器和 FPGA 内部集成的 18 × 18 嵌入乘法器

模拟前端并不能消除回波,信号仍然存在高度混响

实现,并通过流水线技术提高工作频率。符号判决

的特性。图 10 展示了混合结构在 60 mm 厚的铝板 和误差计算模块则采用组合逻辑实现。对该模块进

两侧形成的信道脉冲响应,激励信号如图 10(a) 所

行测试,其回波消除效果如图 10(c) 所示,可以看到

示,为 10 个周期的脉冲信号,接收端的接收信号如

回波得到了一定程度的抑制。

图 10(b) 所示,可以观察到,信号中包含明显的回波

信号和拖尾效应。这些回波信号和拖尾效应导致了 10

码间干扰。为了减小码间干扰的影响,本设计采用 ࣨϙ/V 5 0

-5

了判决反馈均衡器(Decision feedback equalization, -10

DFE)结构。 0 50 100 150

ᫎ/ms

DFE 是一种非线性均衡器,由前馈滤波器 (a) ԧ࠱૱ᑟ٨ᑢф༏ҵηՂ

(Feed forward filter, FFF)和反馈滤波器(Feedback 1.0

filter, FBF)组成。前馈部分用于消除时间上超前和 ࣨϙ/V 0.5 0

滞后的码间干扰,即后面的符号对当前码元的前导 -0.5

-1.0

干扰和前面的符号对当前码元产生的拖尾干扰。反 0 50 100 150

ᫎ/ms

馈部分则用于抵消时间上滞后的码间干扰 [24] 。均

(b) ଌஆ૱ᑟ٨ηՂ

衡器硬件实现结构如图 11 所示,其中 FBF 的输入 1.5

1.0

是判决器的先前输出,通过调整其系数可以减弱当 ࣨϙ/V 0.5

前估计中的码间干扰。DFE 的输出经过符号判决 -0.5 0

-1.0

模块处理,随后通过误差计算模块计算输出信号与 -1.5

0 50 100 150

判决信号之间的误差,并将误差信号送入系数更新 ᫎ/ms

(c) DFE͖ӑՑᄊηՂ

模块。系数更新采用自适应最小均方误差算法,该

算法易于实现且具有较低的复杂度,能够抑制旁瓣 图 10 混合结构的 60 mm 厚铝通道的脉冲响应

效应。DFE 的输入输出关系以及系数更新算法如 Fig. 10 Impulse response of a 60 mm thick alu-

式 (4)所示: minum channel with a hybrid structure