Page 193 - 《应用声学》2025年第3期

P. 193

第 44 卷 第 3 期 杨超等: 基于电磁 -压电混合结构的超声波穿金属通信系统 727

制。经过信号处理后的数字信号被传入数模转换电

2 系统设计

路(Digital to analog converter, DAC),将其转换为

2.1 系统结构 模拟信号。随后,模拟信号经过大电流功率放大器

进行放大,使输出信号的电流增大。最终,该信号用

电磁 -压电混合结构的超声波穿金属通信系统

于驱动EMAT换能器,在金属壁内产生超声波。

由发送端、金属壁、接收端组成。混合结构的超声

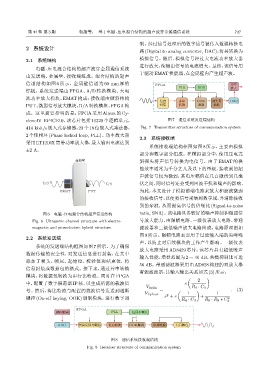

信道结构如图 6 所示,金属壁信道为 60 mm 厚的 FPGA Ҫဋ

PLL DDS ஊܸ

铝板,系统发送端由 FPGA、A/D 转换模块、大电

流功率放大模块、EMAT 构成;接收端由倾斜结构

ηৌ ࣳ˙ OOK ᮕܿᄾ DAC

PUT、微弱信号放大模块、D/A转换模块、FPGA构 ࠰ᜉ ᣁ૱ ូ҄ ฉ

成。这里需要指明的是,FPGA 采用 Altera 的 Cy-

cloneIV EP4CE10,该芯片包括 10320 个逻辑单元, 图 7 通信系统发送端结构

414 kbit/s 嵌入式存储器,23个18位嵌入式乘法器, Fig. 7 Transmitter structure of communication system

2 个锁相环 (Phase locked loop, PLL)。功率放大器

2.3 系统接收端

采用 LT1210X宽带功率放大器,最大输出电流达到

系统接收端结构框图如图 8 所示,主要由模拟

±2 A。

部分和数字部分组成。在模拟部分中,使用压电式

࡛ܞ 斜探头将声信号转换为电信号。由于 EMAT 的换

能效率通常为千分之几及以下的量级,接收到的超

声波信号较为微弱,其电压幅值在几百微伏到几毫

ηՂ ηՂ 伏之间,同时信号还会受到回波干扰和噪声的影响。

EMAT PUT 为此,本文设计了模拟前端电路来放大和滤波微弱

的接收信号,以便将信号采集到数字域,并消除接收

到的杂波,从而提高信号的信噪比 (Signal-to-noise

图 6 电磁 -压电混合结构超声信道结构 ratio, SNR)。该电路具备较好的噪声抑制和微弱信

Fig. 6 Ultrasonic channel structure with electro- 号放大能力,由限幅电路、一级仪表放大电路、带通

magnetic and piezoelectric hybrid structure 滤波器和二级低噪声放大电路组成,电路原理图如

图 9 所示。限幅电路主要用于过滤输入端的尖峰噪

2.2 系统发送端

声,以防止对后续模块的工作产生影响。一级仪表

系统的发送端结构框图如图 7 所示。为了确保

放大电路采用 AD8429 芯片,该芯片具有超低噪声

数据传输的安全性,对发送信息进行封装,在其中

输入性能,增益范围为 2 ∼ 40 dB,共模抑制比可达

添加了帧头、帧尾、起始位、校验位和结束位,将

56 dB。带通滤波器采用由 AD828 构建的双放大器

信息封装成数据包的格式。接下来,通过并串转换

有源滤波器,其输入输出关系如式(3)所示:

模块,将数据包转换为串行比特流。同时在 FPGA ( )

2

中,配置了数字振荡器 IP 核,以生成所需的载波信 s

V bpfin R 4 · C 3

号。然后,将比特流与配置的载波信号发送到通断 = ( ) . (3)

V bpfout 2 1 1

键控 (On-off keying, OOK) 调制模块,进行数字调 s + s + 2

R 4 · C 3 R 5 · R 8 ∗ C

3

FPGA

വલҒቫ PLL ͯՏ൦ካข

ADC ѼхԦᯠکᛦ٨ Ͱᤰฉ OOKᝍូ ˙ࣳᣁ૱ ηৌᝍӊ

图 8 通信系统接收端结构

Fig. 8 Receiver structure of communication system