Page 141 - 《应用声学》2022年第4期

P. 141

第 41 卷 第 4 期 张勇成等: 面向中频段听阈突变听力损失的非均匀滤波器组设计 639

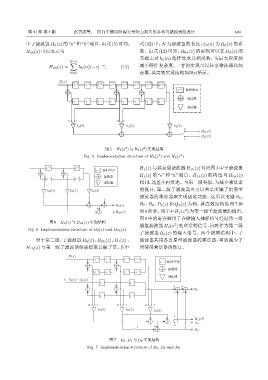

中子滤波器 H 0 (z) 的“o” 和 “h” 端口,由式 (5) 可知, 式 (12) 中,N 为滤波器的长度,h 0 (n) 为 H 0 (z) 的系

H 0h (z)可以表示为 数。由式 (12) 可知,H 0h (z) 的实现可以在 H 0 (z) 的

基础上对 h 0 (n) 选择性求其相反数,为最大程度地

N−1

∑

H 0h (z) = h 0 (n)(−z) −n , (12) 减小硬件复杂度,二者的实现可以共享乘法器和加

n=0 法器,其高效实现结构如图6所示。

X↼z↽

z -1 z -1 z -1 z -1 z -1 z -1 z -1 z -1

z -1 णӭЋ

ҫข٨

z -1 z -1 z -1 z -1 z -1 z -1 z -1 z -1

˲ข٨

h ↼↽ h ↼↽ h ↼↽

4

H ↼z ↽

2

H ↼z ↽

4

2

图 5 H 2(z ) 与 H 2(z ) 实现结构

2

4

Fig. 5 Implementation structure of H 2(z ) and H 2(z )

z -1 z -1 H 1 (z)与其高通滤波器 H 1h (z) 对应图 3中子滤波器

z -1 णӭЋ

ҫข٨ H 1 (z) 的 “o” 和 “h” 端口,H 1h (z) 的构造与 H 0h (z)

z -1 z -1

˲ข٨ 相同,这里不再赘述。与第一级类似,为减少乘法器

的数目,第二级子滤波器也可以共享所属子组原型

h ↼↽ h ↼↽ h ↼↽

滤波器的乘法器来实现级联功能。这里以支路 B 6 、

B 7 、B 8 、P 3 (z) 和 Q 3 (z) 为例,其高效结构如图 7 和

H ↼z↽

图8所示。图7中H 1 (z )为第一级子滤波器的输出。

2

H h ↼z↽

图8 中的寄存器用于存储输入抽样信号经过第一级

图 6 H 0(z) 与 H 0h(z) 实现结构

插值滤波器 H 0 (z )处理后的信号,同时作为第二级

2

Fig. 6 Implementation structure of H 0(z) and H 0h(z)

子滤波器 H 0 (z) 的输入信号。两个级联结构中,子

对于第二级,子滤波器 H 0 (z)、H 0h (z)、H 1 (z)、 滤波器共用各自原型滤波器的乘法器,有效减少了

H 1h (z) 与第一级子滤波器级联提取目标子带,其中 所使用乘法器的数目。

X↼z↽

z -1 z -1 z -1 z -1

z -1 णӭЋ

ҫข٨

z -1 z -1 z -1 z -1

˲ข٨

֓P ↼z↽֓Q ↼z↽

z -1 z -1

B

z -1 z -1

h ↼↽ h ↼↽ h ↼↽

2

H ↼z ↽

B

B

图 7 B 6、B 7 与 B 8 实现结构

Fig. 7 Implementation structure of B 6, B 7 and B 8